台积电宣布已开始通过5nm制造工艺完成制造基础设施来提供风险生产。

将半导体电路制造成晶片时的布线宽度称为制造工艺。随着最小加工尺寸变小,可以在同一区域中布置更多的晶体管和布线。因此,可以实现半导体高速操作。

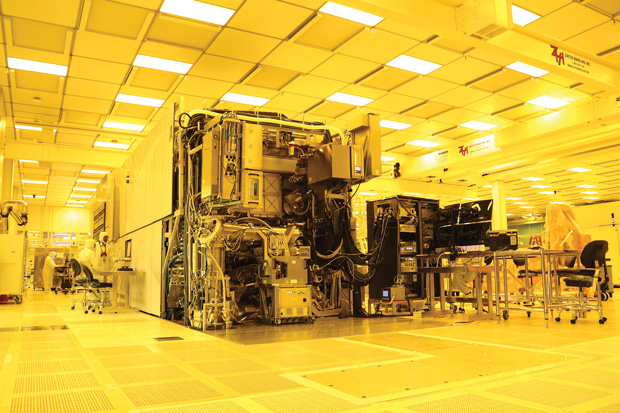

台积电通过其设计板发布的5纳米制造工艺,与公司在极紫外光刻EUV中的7纳米制造工艺相比,可实现1.8倍晶体管密度和15%速度增长的存储器和功率优化。台积电计划为5纳米制造工艺提供5G移动市场和人工智能市场的主要目标。

台积电这次开始是因为在没有收到客户要求的情况下开始生产是危险的,并且需要更多时间才能实现5nm制造工艺的产品上市。向台积电委托半导体生产的苹果公司可能会在2020款iPhone上安装5nm制造工艺芯片。台积电还计划在2022年实现3nm制造工艺。欲了解更多信息,请点击此处 。